【

儀表網 研發快訊】傳統光刻技術主導了當前的平面化工藝制造,但在10納米以下三維結構加工中面臨成本高、工藝復雜等挑戰。自下而上組裝納米結構的方法被視為是可行的替代方案,但液相法主導的組裝常因表面配體污染導致材料純度不足,性能受限,且難以實現復雜三維結構的高分辨率器件的集成。近日,上海科技大學物質科學與技術學院馮繼成課題組通過自主研發的法拉第3D打印技術,在高純惰性氣體環境中以“自下而上”的方式,實現了晶體管的可控制造。相關成果已發表于國際學術期刊Small。

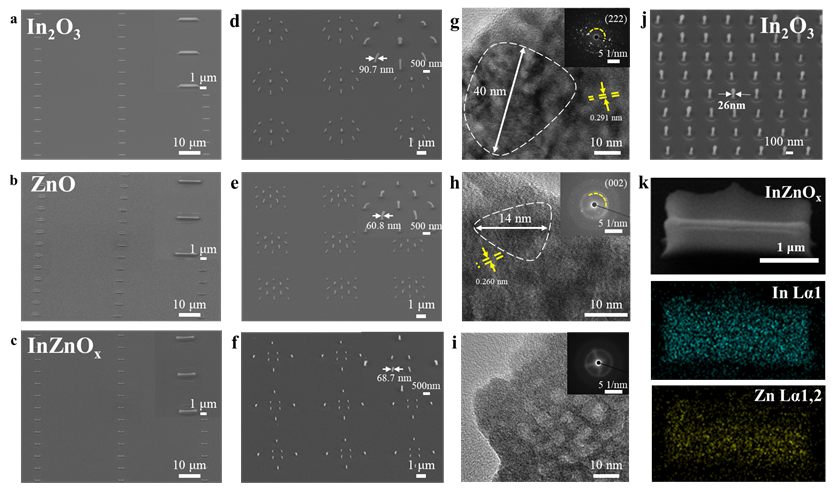

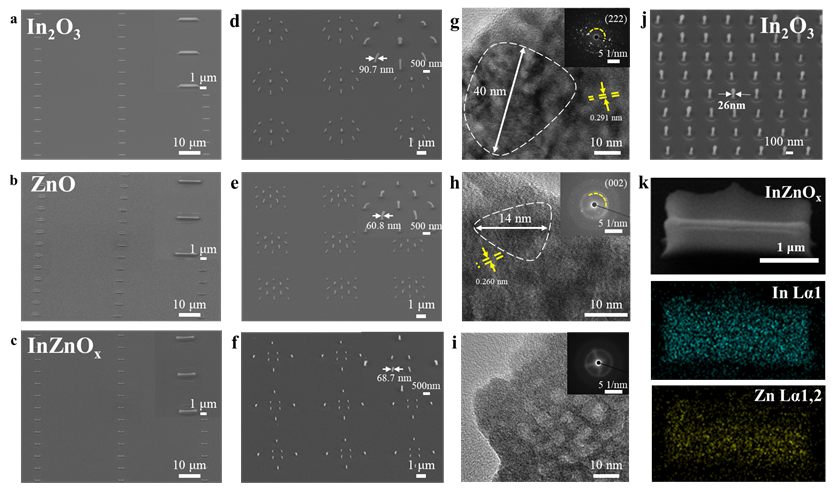

圖1. 氣相法制備的半導體納米顆粒,結晶度高、分散性好

本工作首先在“人工閃電”等離子體環境中,成功制備出多種尺寸約5納米的半導體材料,包括Si、Ge、ZnO、In?O?、InZnO?、GaAs和SiC等。該全干法工藝可有效避免配體污染,保障材料的高純凈度,尤其適用于對空氣敏感的 GaAs、SiC 等材料。研究發現,納米顆粒因超高表面原子比例而呈現類液滴的凝并行為,這一特性有助于在后續打印過程中實現融合生長,保障打印納米結構的半導體性能。

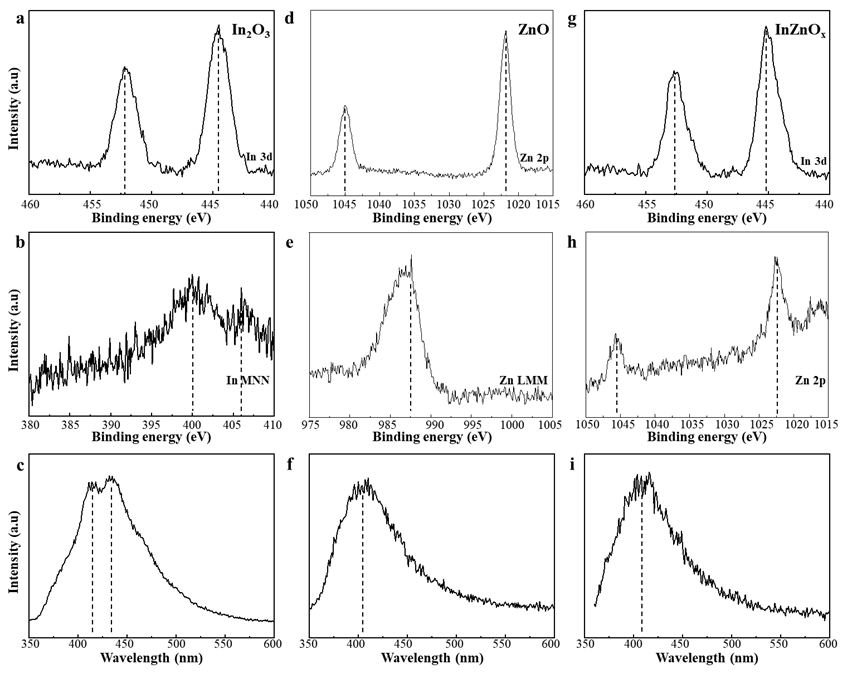

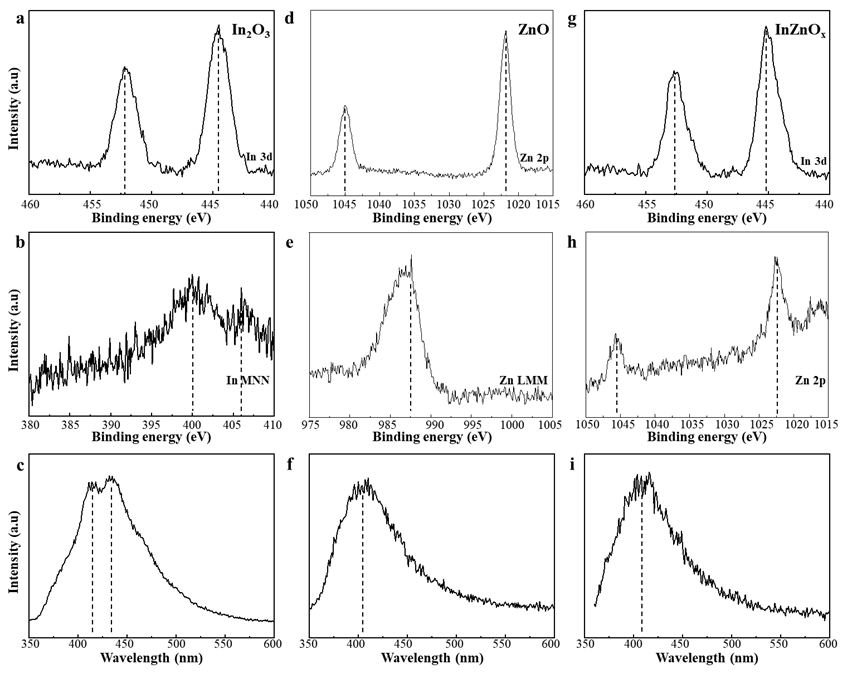

圖2.3D打印的半導體納米Fin及其復雜三維結構

法拉第3D打印技術實現了材料屬性與結構成型的解耦,能夠打印出不同半導體材料但尺度一致的三維納米結構,且這些結構仍可保持良好的本征半導體特性(圖 2、圖 3)。X射線光電子能譜(XPS)和光致發光(PL)光譜分析驗證了打印結構的成分與光學性質。XPS與PL作為互補表征手段,為3D打印半導體納米結構的本征屬性提供了可靠依據。

圖3. 3D打印半導體納米結構材料屬性

圖4. 頂柵和底柵晶體管表征

研究進一步將打印出的氧化銦Fin結構作為溝道,集成到底柵和頂柵FinFET器件中。其中,頂柵控制的場效應晶體管(FET)表現出超過 1000 倍的開關比;經退火處理后,器件載流子遷移率提升至8.33 cm²·V?¹·s?¹。然而,熱處理也導致載流子濃度過高,進而出現了“簡并半導體”行為,使FET喪失了開關功能。為解決該問題,團隊計劃后續通過可控摻雜和尺寸優化進一步提升器件性能。

該研究展示了自下而上、原位打印技術在晶體管制造中的潛力。法拉第3D打印憑借其高空間自由度、納米級分辨率和多材料原位切換能力,為三維芯片結構的可控制造提供了一條無需光刻的新路徑。未來,馮繼成課題組將繼續探索摻雜調控、新結構設計及新材料體系,進一步提升半導體遷移率與晶體管開關性能,推動該技術在微納器件領域實現更廣泛的應用。

所有評論僅代表網友意見,與本站立場無關。