【

儀表網 研發快訊】在集成電路全球化與處理器架構快速演進的背景下,芯片微架構層面的隱私與安全問題始終是硬件系統設計中的關鍵挑戰。隨著RISC-V等新興指令集架構的發展與普及,處理器在高能效與開放性方面取得顯著優勢,但其微架構的新特性也帶來了新的攻擊面和潛在風險。傳統側信道攻擊通常依賴高精度計時指令進行信息提取。近年來,處理器通過限制

計時器訪問以緩解此類威脅,然而,在新興微架構機制下,這些防御措施是否真正消除緩存層的隱私泄露風險仍不確定。因此,開展預防性的微架構分析、逆向與漏洞挖掘研究,對于保障處理器體系安全至關重要。

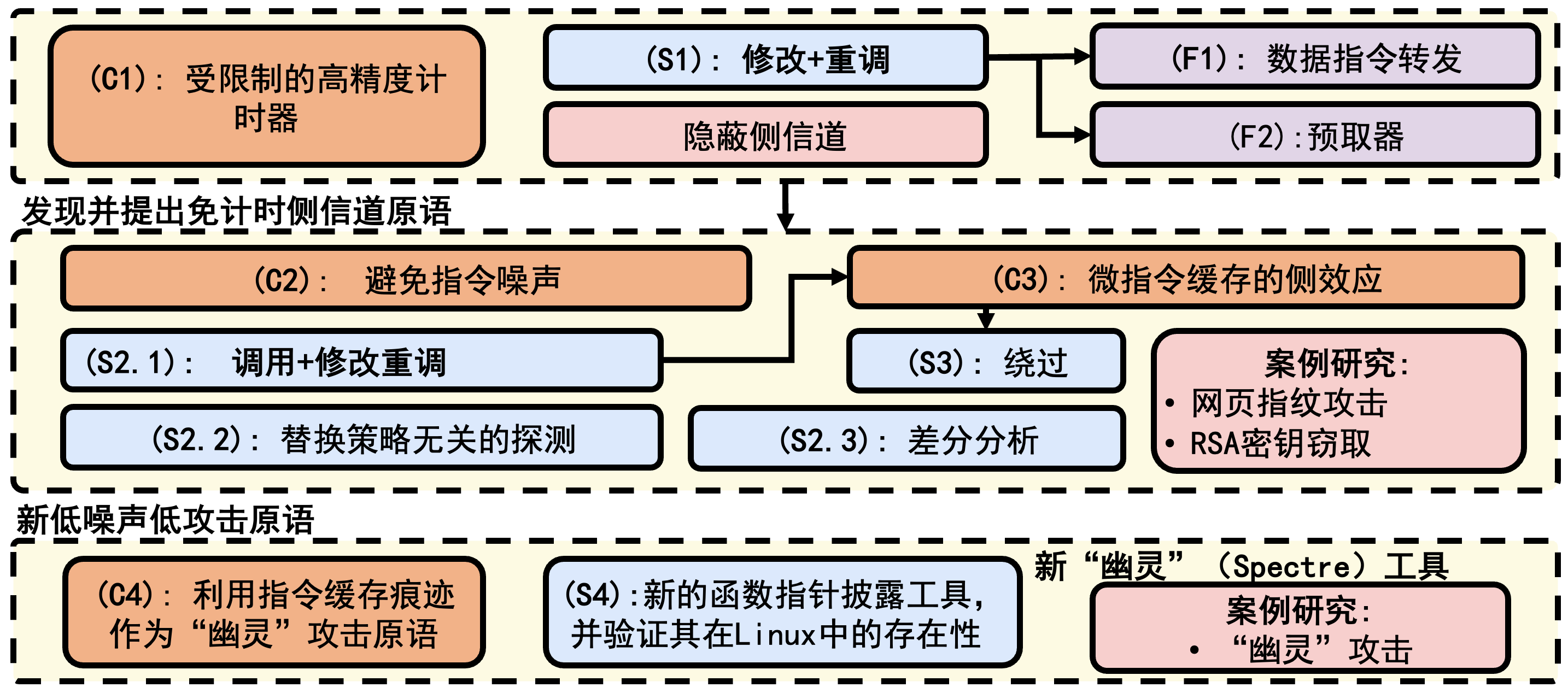

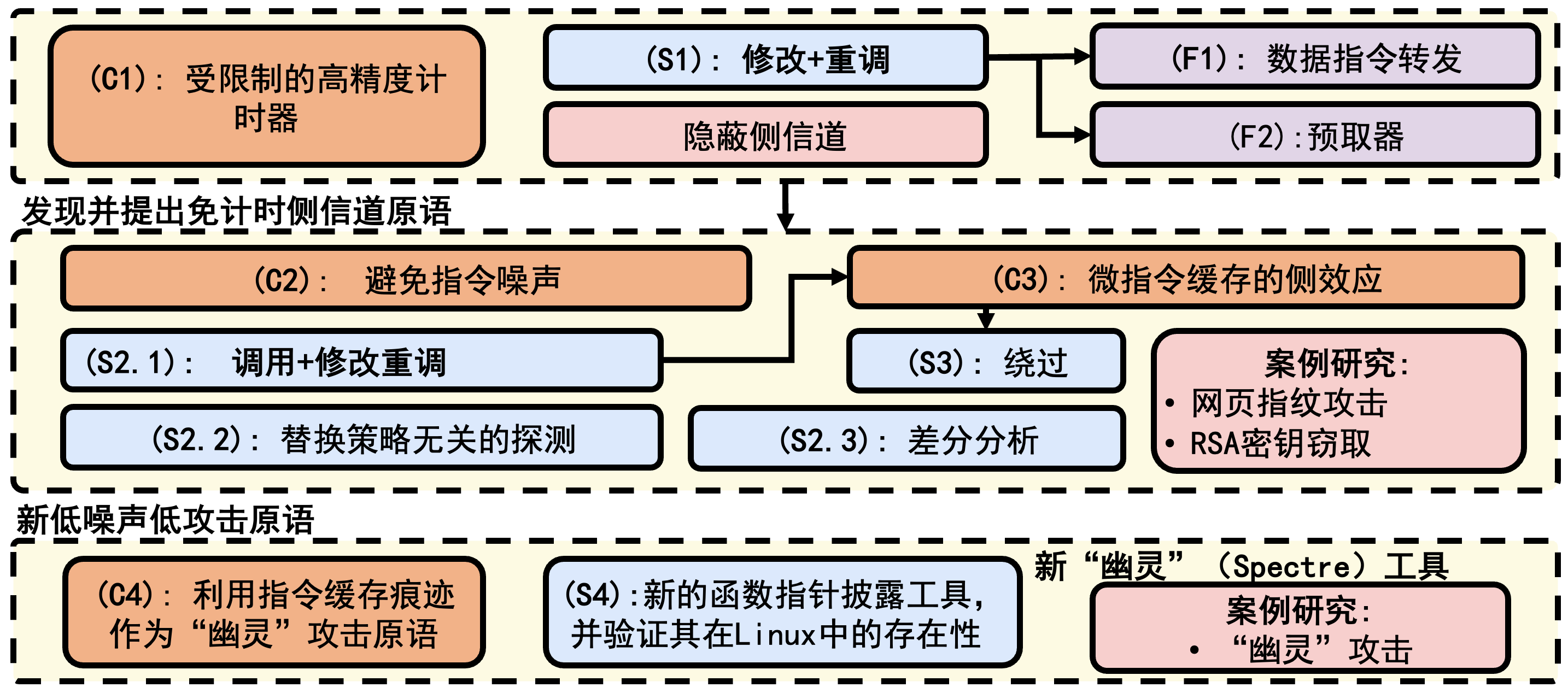

圖1.強弱一致性緩存相關機制逆向與利用

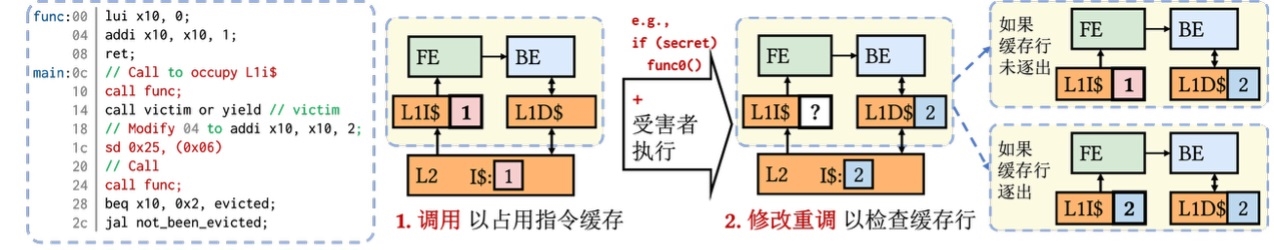

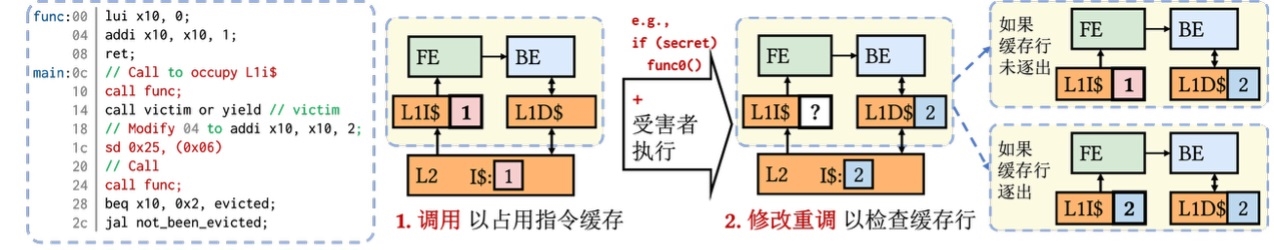

近日,清華大學電子工程系鄧舒文助理教授(劉勇攀、楊華中教授團隊)在免計時緩存側信道安全方向取得重要研究進展。研究通過對多個不同架構的芯片的微架構特性開展的系統性安全分析發現,新興商用與開源架構芯片中普遍部署了弱一致性一級緩存,攻擊者可利用這一特性,繞過現有安全限制,構造免定時器與計數器的緩存攻擊。

基于上述發現,團隊提出了新的攻擊GhostCache(幽靈緩存),并在多個RISC-V與ARM的商用與開源芯片上完成系統性實驗驗證,揭示了弱一致性緩存架構下的安全隱患。基于GhostCache,團隊構建了三類跨安全區域的隱蔽信道(Covert Channel),實現了跨線程、跨特權級甚至跨核心的信息傳輸。該機制進一步被應用于多種攻擊場景中,包括內核數據泄露與加密密鑰竊取。在實際側信道利用層面,研究實現了三類典型攻擊驗證:網頁指紋識別攻擊,即在ARM與RISC-V芯片上均可實現免定時器的瀏覽器硬件緩存狀態監測,100類網站緩存指紋分類準確率超過90%;內核數據泄露攻擊,即包括對內核條件分支執行路徑的重建和Spectre瞬態執行攻擊,團隊基于Linux內核中發現的函數指針調用,構造了首個基于指令緩存的Spectre泄露工具,實現高精度的內核數據泄露;RSA密鑰竊取攻擊,即利用現代密碼算法庫中關鍵路徑的條件分支導致的指令緩存側信道完成密鑰重構。

圖2.利用弱一致性構造數據不一致以實現微架構緩存行狀態觀測

研究提出的GhostCache,不僅揭示了弱一致性架構下的新緩存側信道風險,也為后續的安全防御研究提供了新的關注點。團隊發現的安全問題,是國內首次在商用處理器上發現并披露的免計時緩存側信道攻擊案例,該成果得到業界包括ARM安全團隊在內的廣泛認可,開源領域香山團隊的感謝,也在國際上獲得了SiFive(RISC-V架構主要推動廠商)首個公開漏洞報告感謝。

研究成果以“GhostCache:利用RISC-V和ARM芯片的弱一致性緩存的免計時和計數的緩存攻擊”(GhostCache: Timer- and Counter-Free Cache Attacks Exploiting Weak Coherence on RISC-V and ARM Chips)為題,被第32屆計算機與通信安全會議(ACM Computer and Communications Security 2025, CCS2025)接收。

CCS與USENIX Security、IEEE S&P、NDSS并稱為信息安全領域水平最高、影響力最強的“四大頂會”,也是中國計算機學會推薦的CCF-A類會議。本次會議的錄用率僅為14.5%(315/2186),為近四年最低,收錄的研究成果通常代表著當前網絡空間安全研究進展的最高水平。

清華大學電子工程系2025級博士生金宇為論文第一作者,電子工程系助理教授鄧舒文為論文唯一通訊作者。研究得到國家自然科學基金、中關村實驗室及香山處理器團隊的支持。

所有評論僅代表網友意見,與本站立場無關。